�����ڴ����ʹ洢���ݷ��棬����������Ҫ������������沢�����롣�빦����ص����⣬�������������⣬���������оƬ��ϵͳ��ƣ�������Щ�����ڲ�����������ࡣ

�������ž�����ܶȵ���ߣ���ЩС�����ֿ��ز�����������ͨ����ͳ��ʽ����������������⿴�ƿ��Կ��ƣ����������һ������Ҫ������ҵ��ͬ����������⣬����EDA��˾���Ƴ��豸�����̡���Բ������װ�����ֳ��������������̡����Ϲ�Ӧ�̡��о��Ŷӵȡ�

��������Щ��ı���һ�������Ľ����ǽ����ྦྷ��ܼ��ɵ��̶������ڣ��Լ���֮��������Ҳ��ϼ��ٵĹ���й©ս����FinFET��16/14�������н����©�������⣬�����������ڵ�֮�������ٴγ��֡���3�����Ƴ��У����������ڲ�ͬ��ȫ��Χդ����ЧӦ��(������Ƭ)�ṹ����ʹ����ơ�����������Ͳ��Ա�ø�����ս�Ժͳɱ�����2����/18�������У�Ϊȷ������ܴ����㹻�Ĺ��ʲ����Ⲽ�����⣬���оƬ�����淭ת��������е�Դ���䡣�ڸ�����ˮƽ�У���ҵ���ܻ��ٴθı侧��ܽṹ�����ø��ϳ�ЧӦ�����(CFET)������һ��ʱ�䴰���У��ڶ�պͽṹ�仯����ӿ�֣�ÿ���½ڵ㶼��Ҫ����������⡣

�������磬���Ÿ��ܶ�оƬ�ͷ�װ������չ��˲̬���ݶ����������ܵ���ע����Щ���ݶ��Բ���Ԥ��ķ�ʽ�ƶ�����ʱѸ�٣���ʱ���������һ����Ź������صı仯���仯����40�������У����ýϺ�ĵ���ʡ���������ɵļ�࣬��Щ�����������С�鷳�����ڵ�ǰ��˵��Ƴ̼����У�������Ҫ������ضԴ���Щ���⡣

����Cadence��Ʒ�����ܼ�Melika Roshandell��ʾ��“���ܻ���©���֮ǰ�ļ����������ͣ������幦��ȴ���ߡ����ԣ��������⽫�������أ���Ϊ����һ�����ɵ�·�м����˸���ľ���ܣ�ͬʱ����������ܡ���ϣ������Խ��Խ�ߵ�Ƶ�ʣ�Ϊ����Ҫ��ߵ�ѹ���ġ����ڵ��ܹ��ı���һ�����ߣ������������⽫�����ء����⣬��ʹ�ø�С�ڵ�ʱ��оƬ���Ҳ�ڼ�С�������С���ܹ���������ʱ���ܵ�����������Ӷ�ʹоƬ���ﵽ

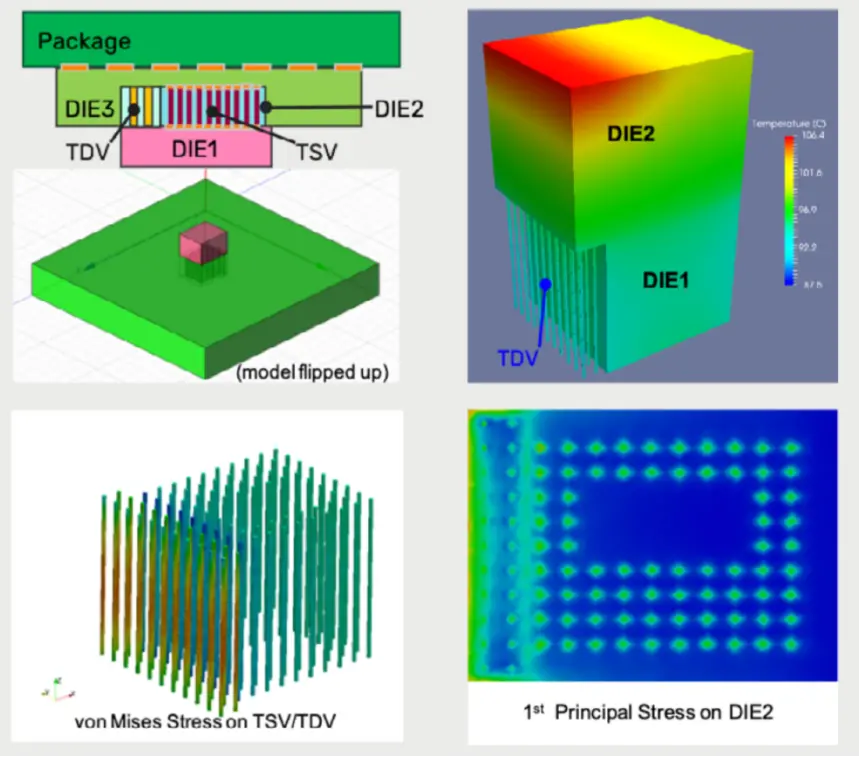

����ͼ1�������е�3D-IC��Ƶ�����ѧ��Ϸ���

������������Ϊ����Ӳ������ʦ��ͬ��ج�Σ�������һЩ���Խ����Ԥ�Ƚ�ģ�Ķ���ѭ����

�����������������ڱ����źŵĵ���ʱ�Ĥ(ʱ�������͵���ʻ��������TDDB)�����ѣ��������˻�еӦ�����Ӷ�����������

������������һϵ�����⣺�����ٵ�Ǩ�ƺ������ϻ�ЧӦ������ʹ����ͨ·��խ�����һ�������˵�·���������������Լ������ź������������ֱ��(������ܵĻ�)�ź�����·�ɡ�

������������Ӱ��洢���������ٶȣ�����ϵͳ�������ܡ�

�������⣬�����������������ź����������Ӱ�죬��������������˲ʱ�ģ���ʹ�÷����������ѡ�

����������Щ���ض���������оƬ������������Ӱ��оƬ��һ���֡�������EDA��ģ��ͻ���ź���֤�����������ϯ��Ʒ����Pradeep Thiagarajan��ʾ��“�Ƚ��⾧��ܺ�������оƬ��IP�����˵��ǣ�������豸�����ȷ�������ͨ����ÿ��MOS��������˲̬�����������ֲ����ȶ���Ƶ�Ӱ�죬Ȼ������¶Ȳ����ݲ���������Ӱ�졣���ڣ�������Խ��Խ�ߵ����ݴ�������Ҫ�������£��������涼��Ҫ���¡���ˣ����õض������Ƚ�����Ͻ��н�ģ�����ܸ��п��ܽ����ЩӰ�죬�������ʵ�����Ƶ�����������ڻ��ڵ�Ӳ�����ϡ������ף�������Ҫ���µ��Ƚ��������ͬʱ�����������ȷ�Ľ�ģ��”

���������������

��������оƬ�����̸տ�ʼӦ����Щ���⣬��Ϊ��оƬ��δʹ�����Ƚ����Ƴ̿�����������оƬԽ��Խ��ر����оƬ��Ԫ��ɣ��������ݶ���Ҫ�ڷ�40nm����߹���ƽ��оƬ�����������½������������Ͳ�����

����ֵ��ע����ǣ���߾�����ܶȣ��������ڵ���оƬ���Ǹ���װ�У�δ�����������ܵ�����Ч;����Ȼ������ȷʵ����߹����ܶȣ�����ʱ��Ƶ�ʡ���ˣ������������������뾧��ܱ���������ء���Щ��������Ӳ��-����Эͬ��ơ������������ͻ��������;�Ե�͵���Ǩ�Ʋ��ϡ����нϸ߾��Ⱥͽ϶ָ̻�ʱ���Ԥȡ������ϡ���㷨�Լ��µĵ�Դ���䷽����

����Arm��˾����ϯCPU�ܹ�ʦVincent Risson��ʾ��“��������ϵͳ��ջ�dz���Ҫ����Ȼ��������Թ�������Ҫ���ף���ϵͳ����������Ҳͬ����Ҫ�������Ϊʲô�����в�ͬ����Ļ��棬���һ���Ĵ�СҲ��ͬ����������һ����Ʒ�мӴ��˻����ģ����Ϊӵ�б��ػ�����ʹ���ε�Դ��������Ϊ�������С�����������չ��3D�����ǿ�������ʹ��3D�ѵ����棬�⽫�����ڼ������ݴ��䲢���Ч�ʡ�”

�����ؼ�����������ڵ�ÿ���������Ч�ʣ�������������Ӳ�������ܽ���ʮ����оƬ��ҵһֱ��עӲ��——����Эͬ��ƣ���ϵͳ��˾ͨ�����ƻ��ܹ����Ȳ������ַ�����ͬʱ���ƶ��豸Ҳ����Ϊ�˾������ƶ�����ӳ����������

����Risson��ʾ��“���ǽ����������������������ܣ�����CPU�����ڽ����һ���ص����⡣���磬���dz����Ľ�����Ԥȡ���棬�����ȷ�Բ������������ݵ���������ˣ������ڱ��ָ��ø��ǵ�ͬʱ�������˻����ϵ�������”

����������������һ���֣����ǻ���Ҫ������������⡣���磬����ʱ������ţ����Ĥ����������������ܵ���ͬ�������ػ��������ļ��٣��������ڳ���оƬƬ��Ʒ�ķ�װ�ڲ���Ansys���ӡ��뵼���ѧ��ҵ�����о�Ա����ϯ����ר��Norman Chang��ʾ��“����������Ҫ��������ڶ���źź������ڲ�ͬ��ѹ�µĶ�������磬ʱ�������(TDDB)��Ϊһ�����⡣���һ����������һ����ͬ��ѹ���ź��������ڣ���ô�����Ͼͻ��Ӧ����ͬ�ĵ�ѹ��������ʱ������ƣ������ʱ��Ľ�������������һ�������⣬������Ҫ�ҵ�������Ľ���취��”

������һ��������

�������ݶ�Ҳ��һ����ս���ر��ǵ����DZ仯�������ڲ�ͬ�������ؼ��нϴ����ʱ�����������2.5D�������Ϊ���ԣ����ܵ��±��Ρ���Ԥ����δ�������Ƴ���3D-ICs��Ҳ����ͬ�����⡣������������£��������ܻᱻ��ס���Ӷ�������ѩ��ЧӦ��

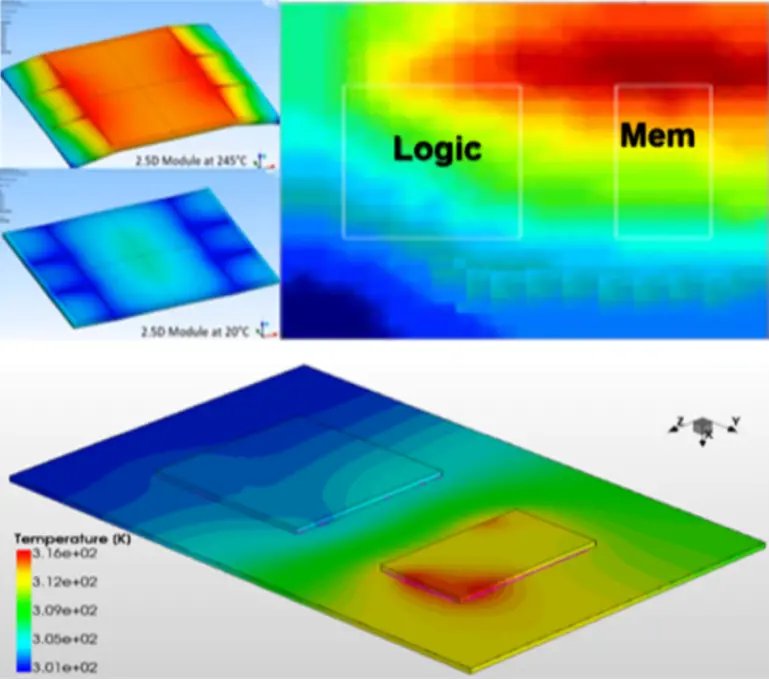

����ͼ2��2.5D ���ɵ�·������ѧ����ѧ���������չʾ���¶��ݶȣ�������245°Cʱ���������

�����ű�ʾ��“��3D-IC�У��������¶��кܴ�Ĺ�ϵ�����¶�����ʱ��©�繦�Ľ����ӣ����ݶȷֲ���Ϊ3D-IC�ж����������ĺ��ġ��¶Ȼ�Ӱ�칦�ģ�ͬʱҲ��Ӱ����衣���¶�����ʱ������Ҳ�����ӣ���Ҳ��Ӱ���糣���������ź������Ժ��������Բ���Ӱ�죬ͬʱ����Ӱ��Ӧ������3D-IC�л��ʹ�����ֺ�ģ��ʱ��ģ�ⲿ�ֶ�Ӧ�������С�����Ҫ֪�����ݶȺ��ȵ��λ�ã��Ա㽫ģ��Ԫ��Զ���ȵ㡣����㿴��ģ��Ԫ������ѭ�����豸���ϻ��ٶȻ�ӿ죬��Ὺʼ���������ʧ�䣬ģ���·��Ч���������������Ѹ���½���”

���������ֻ�ǿ�ʼ����˼�Ƽ�(Synopsys)�IJ�Ʒ�������ܼ�Kenneth Larsenָ�������ѵ�оƬ�и���Ԫ�ص�λ�ð��Ŵ�����ܻ����һЩ���벻�������⣬�����Ƚ�����ţ���Ҳ���ܻή���������ܡ�“�����Ѵӵ�Ƭ���ת�������Ƭ����ƣ���ʹ�ø����豸֮��ľ�����С�ˣ����ǿ��Ի���Ӱ�졣��һ���豸�ѵ�����һ���豸��ʱ���������ɢ����ȥ?����һ�������ս������3D-ICs����һ���������ܷ����нṹ�����Ե�ϵͳ��ͬʱ���㻹���ע�����Ļ�е���Ⱥ�������——ؽ�����������ʵ��̫�ࡣ”

�����ڹ�ȥ������������������ǽ��͵�ѹ��Ȼ�������ַ�ʽ�Ѿ���ò�����Ч����Ϊ�ڼ��͵�ѹ��״̬�£������쳣����Ϳ��ܵ������⡣Fraunhofer IIS����Ӧϵͳ���̲�����Ʒ�������Roland Jancke˵��“���ڵ��ļ���(���ٽ�����ٽ�����)�߹����豸��˵��������һ���ؼ����⡣����һ��������������⣬��Ϊ��ģ���������ͨ��������֣���������ʵ�����б�¶��������������������ʵ�г���ʱ������Ҫ�˽ⲢӦ������”

�����Խ������Ϊ��������ƽΣ����ڻ����в����������������ײ����Jancke��ʾ��“�����ڼ���ǰ�Ϳ�ʼʹ�û���ģ�������о������ڵĽ������״������ʱ��ע���ص��ǵ����豸������Χ���豸��Ȼ�����������������ͨ��������ϵġ������Զ������εĽ���������⡣”

������������Ҳ�ᵼ��DRAM�г������⣬�ر����ڱ��ص�Ԫ�ܶ�����ʱ���������ܵ�����Ӱ�졣��������������ѧԺ�ļ������ѧ����Onur Mutlu��ʾ��“�϶����������������⣬�������һ����Ԫʱ�����ڵ����л���ԭ���µĵ���Ż��ڽṹ�в��������������Ƿ��ʾ���ܡ����ּ�����Ϊ��������������¿ɿ������⡣���dz�֮Ϊ��Ԫ����š��д�������һ�����ӣ�����һ��ʱ��������ڵ��С�RowPress����һ�����ӣ��㳤ʱ�䱣��һ�д�״̬�����Ӱ�쵽���ڵ������С��������Ǽ�Сÿ����Ԫ�Ĵ�С����С��Ԫ��ಢ����ܶȣ����ֵ�Ԫ����������Խ��Խ�ձ顣����ܻᵼ���������������������������ʵ�����з����������”

�����ڹ��ķ��棬�ܻ����һЩ���벻�������⡣Movellus�Ĺ��ļܹ�ʦBarry Pangrle��ʾ��“���ۺ���ʱ��Ƶ�ʣ���ϣ������͵�ѹ�����У��Ա������ٵ��������������ǿ��Խ���һ���̶ȵ�ģ�ͣ����ܻ�����һЩ������������Զ�һ��оƬ�ڲ�ͬ�����µ�����ѹ��Ƶ�����������ڲ�ͬ�����µı��֡�����������Щ���ݣ���Ҫ��Ϊ�����������ʵ��������ã�����һ�����������������Dz��������ÿ��оƬ������������ô�����Ƿ�Ҫ��оƬ���з��࣬����‘������������оƬ�������ʱ�Ӻ������ѹ�����С�’���⣬����ϸ�ڵ�ѡ��ȡ�������۸�оƬ�ij��̡�”

������������

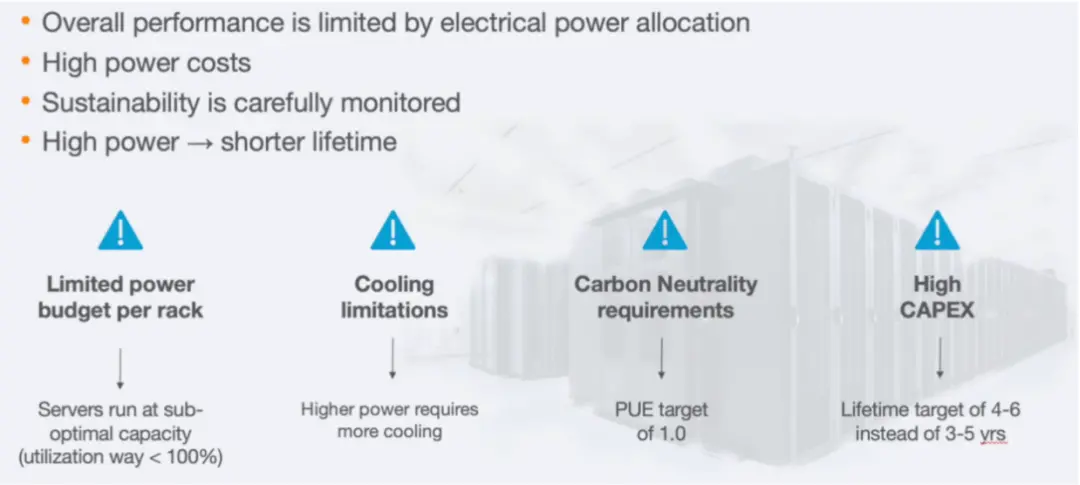

�������Ļ��漰���ʽ�������⣬�����Ӵ�����������������Դ�����������ĺĵ����Ķ��١�������ܶ�Խ�ߣ��������������ͽ��������������Խ�ࡣ�ڸ������͵��˹�����Ӧ���У�Ŀ��������ȵ���߾���������ʣ��ⷴ���������ĸ�������������������������ͬʱ��Ҫ�������ȴ��

����proteanTecs���̽���������ܲ�Noam Brousard��ʾ��“��ЩӦ����Ҫ�����������������ָ������������Ч�ĵ����������ս�Ϊ�������Ĵ��������Ľ�ʡ����������Ҫ�ġ����⣬���ǻ�Ҫ��עӦ�öԻ�����Ӱ�죬��ϣ���ӳ����Ӳ�Ʒ��ʹ��������”

����ͼ3�����Ķ�оƬ��Ӱ��

����������ص�Ӱ�첢��������оƬ������Cadence��Roshandell��ʾ��“��2.5D����У���Ӧ���ᵼ���������Ӷ����ӿ��ܻ��ƻ����ӻ����PCB֮�亸��ķ��ա�һ�������ѷ죬�ͻ���ֶ�·���Ӷ����²�Ʒ��������������ˣ���ν����������Լ���ν�ģ������Ҫ����������Ƶ��������ǰ���ǵ���һ�㲢��ȡ��Ӧ��ʩ��”

������3D-ICs�У������ø��Ӹ��ӡ��ٴ�ǿ��������������ڷ����������Ҫ�ԣ�����3D-ICs�У������ۼ�ЧӦ��Ansys���ű�ʾ��“��SoC��ȣ���̬���ع�����3D-ICs����ķdz����֡����DZ��뾡�翼�������ܹ�����Ϊ�������һ��3D-IC����15��Ƭ��оƬ����ô�������15��Ƭ��оƬ֮����书������Ӧ��̬��������ʱ��ά����?�ڲ�ͬ��ʱ�̣�ij��Ƭ��оƬ���ܻ��в�ͬ�Ĺ������أ�����ܻ�����ȵ㡣�����������Ƭ�оֲ��ȵ㣬�ײ���ƬҲ�оֲ��ȵ㣬�������ֲ��ȵ���ij��ʱ������ʱ������ȵ㽫���ȫ���ȵ㡣���������Ƭû���л���ȫ���ȵ���ܱȾֲ��ȵ�߳�10��15���϶ȡ�����3D-IC��·���ʦ��ȫ���ֲ�������Ϊ�����3D-IC�е�һ��Ƭ��оƬ����ģ��ʱ�������������ʵ�Ĺ������̶�����3D-IC����ģ�⡣”

�����������ڣ�������������������أ���Ҫ��ij�ֱ�����������������ǵ¿Ƽ���ƺͷ����Ʒ�鸱�ܲü��ܾ���Niels Faché��ʾ��“���������Ż���Щ�豸������ܻ��ע���������Ŀ�꣬��������¶ȡ�����ɢ����������Ҫ�ڻ�еӦ���ı�����������Щ���⡣����뽨����Щ��������ЧӦ��ģ�͡��������֮���ϵ�dz����ܣ�����Ҫ�����Ϸ������ʽ���С��ٸ����ӣ����Dz��õ��ȷ��档���ԣ����۲���������ܵĵ���ʱ���������������Ӱ�졣���ţ�������Ӱ��������ԣ������ı������Ϊ������Ҫ����Щ����ý�ģ��”

�����������

���������빦����ص����⣬û�е�һ��ȫ��Ľ�����������кܶ��ܽ����������ķ�����

������������һ��������Ҳ������ķ������������ƹ�����ơ�Rambus�о�Ա�ͽܳ�������Steven Woo��ʾ��“һ�ж�ʼ�ڹ�עĿ��Ӧ�ó������Լ���������Щ��������Ĺ��ܡ���ͼ���Ӹ��ֹ�������������DZ���г���ʹ�ó�����������ܺ����ˣ����������ᵼ��оƬ��������ĺ����Ե����ӣ��Ӷ�Ӱ��оƬ��ҪӦ�õ����ܡ����DZ����ϸ���������й��ܣ��Լ�����ս�Ե��ж������Ƿ�������Ҫ������оƬ�С�ÿһ���¹��ܶ���Ӱ�쵽PPA(���ġ����ܺ����)�����ʼ�չ�עĿ���г���ʹ�ó����ǵ�һ����”

�����⽫�����幦�IJ�������Ӱ�죬�ر�����AI����Woo��ʾ��“��AI��������������Ҫ���ǣ������Ƕ��ڱ�Ե�豸��һЩѡ�����оƬ���緽ʽ��ɢ�����ơ��Ƿ���Ҫ֧��ѵ����/������������Ҫ��оƬ��������Ļ����Լ�֧�ֵ����ָ�ʽ�ȡ�֧�ִ������ܼ���ζ�Ÿ����������ģ��Լ��ڹ���δʹ��ʱ���ӽ�ֹ�ĸ����ԡ��������ݴ���Ӱ�����ܲ����Ĵ�������Ԥ�㣬���ʦ��Ҫ����˽��ڿ����ܹ�����ȵؼ��ٱ�Ե���ݴ���ļܹ�ʱ��Ҫ�ƶ��������ݡ�”

������һ�ַ����Ƕ���ƽ���ʵ�ʹ������ز��ԡ���˼�Ƽ��ĵ��Ľ��������Ʒ�������ܼ�William Ruby��ʾ��“��Щ�ͻ����ڳ������������д����ԵĹ������أ���Ϊ���Dz�֪������ʲô��֪�����¡�” ������ǹ��ĸ��ǡ�“������Ϊʲô��������dz�����������?������Ϊʲô���Ŀ��и����Ǻõ�?” �����Dz�֪�����ǣ��µ��������¿�����θı������������ϣ�����ֱ仯�ǽ���ʽ�ģ����������Ѿ�Ϊ������Ԥ�㣬�����DZ��۵ع��ڱ��ء��������Ԥ��̼����»ᷢ��ʲô�仯��?

�������湩������һ��ѡ�������������Ƚ��Ľڵ��ϡ�“��ij�̶ֳ��ϣ������������ݼ������⣬��Ϊ����Ҫ�����Ӷ��㵽�ײ�IJ��ϣ������������ǹ���ͽӵز��ߣ�”Movellus��Pangrle��ʾ��“�������Դӱ���ʵ�ֹ��磬�����ش���������17�������㣬��ô��Ͳ���Ҫ�����ܶ���ˡ��ܹ��ƹ�����������ջ���ӱ���ӽ�����ܣ��Ӷ����ص��Ĵ������еĹ��ף������������ҵ��ħ����”

������оƬ�ͷ�װ�ڲ�ʹ�ô���������빦�������Ϊ�ı仯����һ�ַ�����proteanTecs��Brousard��ʾ��“����ʵӦ���У����������ػή�����ܣ�������DZ���Ԥ���ѹ������������֪���������������ȵĹ��������Լ�оƬ���ϻ�����������Щ������ʹ��������������Ӧ�ô���VDDmin�ĵ�ѹ��”

�������⣬ͭ�߿������ڴ�������������ɢ�ȵĵط�����˼�Ƽ���Larsen��ʾ��“����Բ�ȡ��ʩ�������Ż��ѵ�оƬ�е�TSV���֣�Ҳ����ʹ���ȹ��ס���dz����ӣ���EDA����һֱ�ڴ���ָ�������⡣����������Ҫ����ġ����ǣ������뻺��ijЩ����ʱ������Ҫ����һЩ��������Ȼ���ܻ�Ӱ�쵽ijЩ�������õ��ļ�ֵ����������Ҫ����ġ�Ϊ�˿ɿ��ԣ�����ܻ��������࣬�������Ƕѵ��е�TSV���ϼ��ϡ�”

��������

������ȥ��ʮ����������һֱ��ͷ��оƬ�����̵�һ�����⡣�����ֻ��ᷢ�����й��ȵľ��棬������ȴ����֮ǰ�رա�����ͬ����ԭ��һ�����������ܿ��ܻὫ����ת�Ƶ���һ�����ܡ���оƬԽ��Խ��ر��ֽ�ɸ����������װ��һ��������������ҵ��ʼ����5�������µ�оƬ���������⽫�ڸ���������֡�

�����ܹ������ֲ��ߡ��ź������ԡ����ȡ��ɿ��ԡ��������Ժ��ϻ����빦�Ľ�����ء�����оƬ��ҵ�����Զ��صķ�ʽ�Լ���ͬ�Ĺ�����Ӧ�Զ��ص��г���������ҵ����Ҫѧϰ��δ��������빦����ص�Ӱ�졣�ڹ�ȥ��ֻ�в�����ߵ�оƬ�����̲Ź��Ĺ��ģ������ڱ�ò�ͬ���ǿ��Ժ��Թ�����Ƶ�������Խ��Խ�١�

��������Դ���뵼���ҵ�ݺ

�����������ݽ����Ķ���������Ͷ�ʽ��飬������Դ���Ͷ���߾ݴ˲����������Ե���

��ʮ�Ĵ�Ӣ�ض�® ���™ ������(����Raptor Lake S Refresh)�������Ƚ���Intel 7�Ƴ̹��ա�

��ά����(AVC)����������ʾ��2024��1-9�������������۶�94.2��Ԫ��ͬ������3.1%�����ж��������������죬ͬ����14%���Ƿ�����ͳ���������»���ͬ�Ƚ���2.3%��

����ǰ��Ҫȥ���ڰ죬һ������������Ҫ������ˣ����ڷ������!�������칫������С��������ʾ�����ύ��ز��ϣ��������ӣ�����������ij���˻��ʹ����21600Ԫ��

��˶ProArt����27 Pro PA279CRV��ʾ����ƾ����������������ú;���ɫ�ʳ���������Ϊ���Ĵ�����������ʵ���Եİ�����˫ʮһ�ڼ����2799Ԫ���Լ۱Ⱥܸߣ���ֱ�Ǵ������ǵ���ѡ��

9��14�գ�2024ȫ��ҵ��������ᡪ����ҵ��������ʶ����ר����̳�������ɹ��ٰ졣